The Intel Quartus Prime software includes everything you need for designing FPGA, SoC, and CPLD from Intel. This suite has been specifically designed and developed for designing and programming the PLDs from this company.

Undoubtedly, using this software and its capabilities in complex designs and millions of logical elements clearly demonstrates its potential and gives the designer the opportunity to implement new ideas and create innovative designs.

Key Features of Intel Quartus Prime: – Partial Reconfiguration:

Partial Reconfiguration (PR) allows you to dynamically reconfigure part of the FPGA while the rest of the FPGA design process is still running.

This methodology is effective in systems where multiple functions use the same FPGA resources.

– Rapid Recompile:

Rapid Recompile is an optional step in the Intel® Quartus® Prime compilation flow, where the compiler, if possible, reuses the previous merge and fitting results and does not reprocess unchanged design blocks.

The Rapid Recompile feature supports functional ECO changes based on HDL, allowing you to reduce compile time.

– Block-Based Design Flows:

Intel® Quartus® Prime Pro Edition offers block-based design flows.

Two types of design flows can be implemented in this software: incremental and block reuse design flows, both of which make collaborative design in a team easier.

– Step-by-Step Incremental Optimization:

In the Intel® Quartus Prime Pro Edition, to provide more control over the design flow, the traditional fitter phase is broken down into more specific stages, with optimization being possible at each stage.

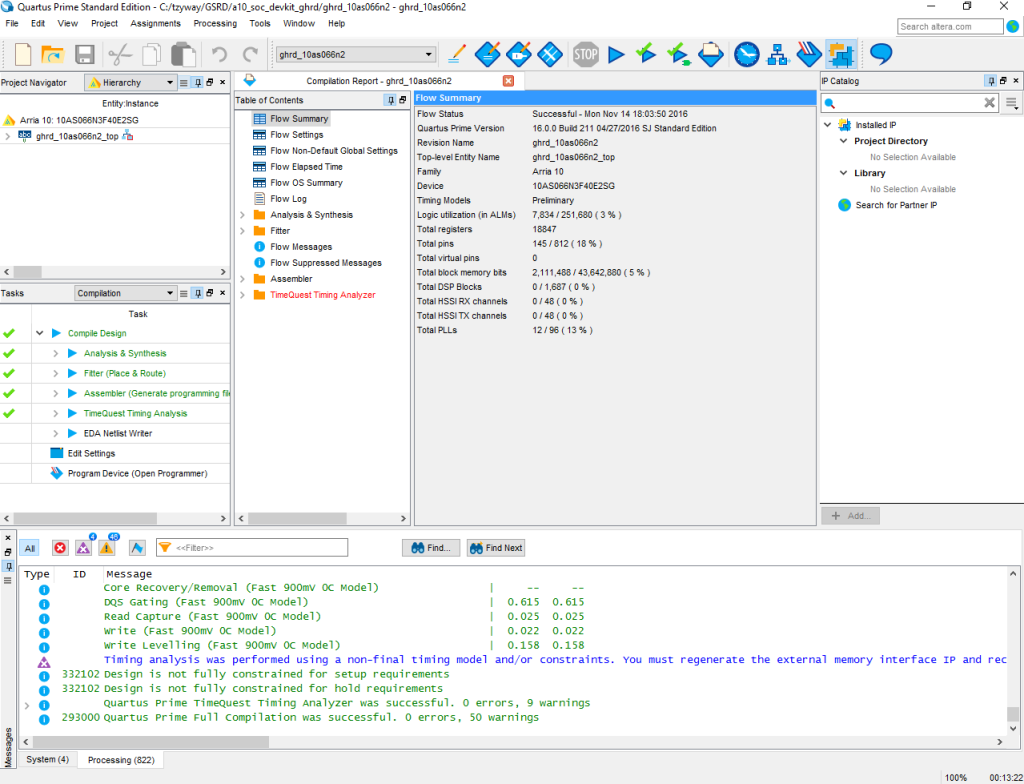

Intel Quartus Prime Pro

Features and Capabilities of Altera Quartus Prime:

Qsys: The next generation of system integration tools. This tool saves significant time and effort in the FPGA design process.

Powerplay Power Analyzer: The ability to estimate power consumption from the initial design concept through design execution.

System Console: A system-level debugging tool that helps you debug FPGA designs in real-time quickly.

Synthesis: The new synthesis engine, which integrates a new language parser into the software. With this parser, designers can view the enhanced RTL language.

External memory interface tools for identifying calibration issues and measuring margins for each DQS signal.

DSP Builder: A tool for seamless integration between MATLAB/Simulink and Quartus II software.

SoCEDS: A set of development tools and helpful applications for developing SoC FPGA system software.

Evaluation of high-speed serial link performance.

A comprehensive set of design tools for Intel’s PLDs.

Increased speed during partial reconfiguration for Intel® Stratix® 10 devices.

The ability to use both the command-line interface and the graphical user interface for collection and analysis.

Hierarchical partial reconfiguration.

Partial reconfiguration simulation that allows you to view changes and intermediate effects in a reconfiguration partition.

Signal Tap logical analyzer debugging.

Rapid recompile to reduce compile time.

Support for block-based design flows.

Step-by-step optimization for convergence in design operations.

Process integration and reduced time and energy in FPGA design.

Simulation of design execution from Concept samples.

Debugging and troubleshooting FPGA designs.

Development and design of various SoC.